Diego Nehab

Most Recent Affiliation(s):

- IMPA

Other / Past Affiliation(s):

- Princeton University

Location:

- Rio de Janeiro, Brazil

Learning Category: Jury Member:

Learning Category: Presentation(s):

Type: [Technical Papers]

Converting Stroked Primitives to Filled Primitives Presenter(s): [Nehab]

[SIGGRAPH 2020]

Type: [Technical Papers]

Automating Image Morphing Using Structural Similarity on a Halfway Domain Presenter(s): [Liao] [Lima] [Nehab] [Hoppe] [Sander] [Yu]

[SIGGRAPH 2014]

Type: [Technical Papers]

A system for high-volume acquisition and matching of fresco fragments: reassembling Theran wall paintings Presenter(s): [Brown] [Toler-Franklin] [Nehab] [Burns] [Dobkin] [Vlachopoulos] [Doumas] [Rusinkiewicz] [Weyrich]

[SIGGRAPH 2008]

Type: [Technical Papers]

Fast triangle reordering for vertex locality and reduced overdraw Presenter(s): [Sander] [Nehab] [Barczak]

[SIGGRAPH 2007]

Type: [Talks (Sketches)]

The real-time reprojection cache Presenter(s): [Nehab] [Sander] [Isidoro]

[SIGGRAPH 2006]

Learning Category: Moderator:

Type: [Technical Papers]

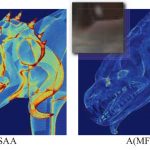

AMFS: adaptive multi-frequency shading for future graphics processors Presenter(s): [Clarberg] [Toth] [Hasselgren] [Nilsson] [Akenine-Moller]

[SIGGRAPH 2014]

Type: [Technical Papers]

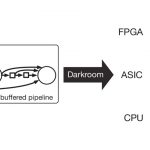

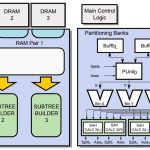

Darkroom: compiling high-level image processing code into hardware pipelines Presenter(s): [Hegarty] [DeVito] [Brunhaver] [Ragan-Kelley] [Bell] [Vasilyev] [Cohen] [Horowitz] [Hanrahan]

[SIGGRAPH 2014]

Type: [Technical Papers]

Embree: a kernel framework for efficient CPU ray tracing Presenter(s): [Wald] [Woop] [Benthin] [Johnson] [Ernst]

[SIGGRAPH 2014]

Type: [Technical Papers]

Extending the graphics pipeline with adaptive, multi-rate shading Presenter(s): [He] [Gu] [Fatahalian]

[SIGGRAPH 2014]

Type: [Technical Papers]

RayCore: A Ray-Tracing Hardware Architecture for Mobile Devices Presenter(s): [Nah] [Kwon] [Kim] [Jeong] [Park] [Han] [Manocha] [Park]

[SIGGRAPH 2014]

Type: [Technical Papers]

A hardware unit for fast SAH-optimised BVH construction Presenter(s): [Doyle] [Fowler]

[SIGGRAPH 2013]

Type: [Technical Papers]

A sort-based deferred shading architecture for decoupled sampling Presenter(s): [Clarberg] [Toth] [Munkberg]

[SIGGRAPH 2013]

Type: [Technical Papers]

Analytic Displacement Mapping Using Hardware Tessellation Presenter(s): [Nießner] [Loop]

[SIGGRAPH 2013]

Type: [Technical Papers]

Cardinality-constrained texture filtering Presenter(s): [Manson] [Schaefer]

[SIGGRAPH 2013]

Role(s):

- Talk (Sketch) Presenter

- Technical Paper Moderator

- Technical Paper Presenter

- Technical Papers Jury Member

If you find errors or omissions on your profile page, please contact us: historyarchives@siggraph.org

Did you know you can send us a photo of yourself and a bio and we will post it? Make sure the photo is at least 1000 x 1000 and send it to the email above along with the bio and we will add it to your page.