“Graphics for the masses: a hardware rasterization architecture for mobile phones” by Akenine-Moller and Strom

Conference:

Type(s):

Title:

- Graphics for the masses: a hardware rasterization architecture for mobile phones

Presenter(s)/Author(s):

Abstract:

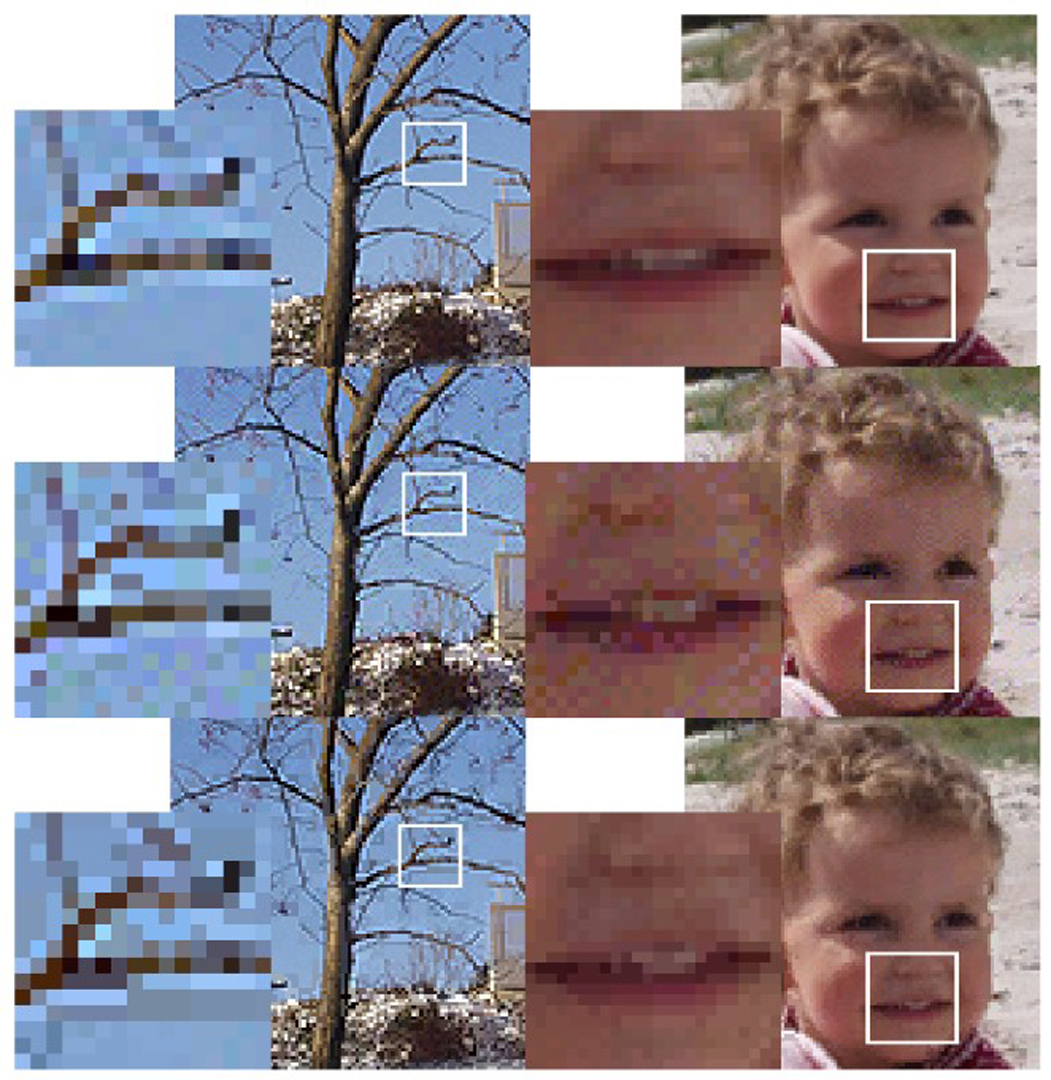

The mobile phone is one of the most widespread devices with rendering capabilities. Those capabilities have been very limited because the resources on such devices are extremely scarce; small amounts of memory, little bandwidth, little chip area dedicated for special purposes, and limited power consumption. The small display resolutions present a further challenge; the angle subtended by a pixel is relatively large, and therefore reasonably high quality rendering is needed to generate high fidelity images.To increase the mobile rendering capabilities, we propose a new hardware architecture for rasterizing textured triangles. Our architecture focuses on saving memory bandwidth, since an external memory access typically is one of the most energy-consuming operations, and because mobile phones need to use as little power as possible. Therefore, our system includes three new key innovations: I) an inexpensive multisampling scheme that gives relatively high quality at the same cost of previous inexpensive schemes, II) a texture minification system, including texture compression, which gives quality relatively close to trilinear mipmapping at the cost of 1.33 32-bit memory accesses on average, III) a scanline-based culling scheme that avoids a significant amount of z-buffer reads, and that only requires one context. Software simulations show that these three innovations together significantly reduce the memory bandwidth, and thus also the power consumption.

References:

1. AKENINE-MÖller, T., AND HAINES, E. 2002. Real-Time Rendering. AK Peters Ltd. Google Scholar

2. COX, M., AND HANRAHAN, P. 1993. Pixel Merging for Object-Parallel Rendering: a Distributed Snooping Algorithm. In Symposium on Parallel Rendering, ACM SIGGRAPH, 49–56. Google Scholar

3. FROMM, R., PERISSAKIS, S., CARDWELL, N., KOZYRAKIS, C., MCCAUGHY, B., PATTERSON, D., ANDERSON, T., AND YELICK, K. 1997. The Energy Efficiency of IRAM Architectures. In 24th Annual International Symposium on Computer Arhchitecture, ACM/IEEE, 327–337. Google Scholar

4. GREENE, N., KASS, M., AND MILLER, G. 1993. Hierarchical Z-Buffer Visibility. In Proceedings of ACM SIGGRAPH 93, ACM Press/ACM SIGGRAPH, New York, J. Kajiya, Ed., Computer Graphics Proceedings, Annual Conference Series, ACM, 231–238. Google Scholar

5. HAKURA, Z. S., AND GUPTA, A. 1997. The Design and Analysis of a Cache Architecture for Texture Mapping. In 24th International Symposium of Computer Architecture, ACM/IEEE, 108–120. Google Scholar

6. IGEHY, H., ELDRIDGE, M., AND PROUDFOOT, K. 1998. Prefetching in a Texture Cache Architecture. In Workshop on Graphics Hardware, ACM SIGGRAPH/Eurographics. Google Scholar

7. KELLEHER, B. 1998. PixelVision Architecture. Tech. rep., Digital Systems Research Center, no. 1998-013, October.Google Scholar

8. KLEIN, A., LI, W., KAZHDAN, M., CORRÊA, W., FINKELSTEIN, A., AND FUNKHOUSER, T. 2001. Non-Photorealistic Virtual Environments. In Proceedings of SIGGRAPH 2000, ACM Press/ACM SIGGRAPH, New York, E. Fiume, Ed., Computer Graphics Proceedings, Annual Conference Series, ACM, 527–534. Google Scholar

9. LATHROP, O., KIRK, D., AND VOORHIES, D. 1990. Accurate Rendering by Subpixel Addressing. IEEE Computer Graphics and Applications 10, 5 (September), 45–53. Google ScholarDigital Library

10. MCCABE, D., AND BROTHERS, J. 1998. DirectX 6 Texture Map Compression. Game Developer Magazine 5, 8 (August), 42–46.Google Scholar

11. MCCORMACK, J., AND MCNAMARA, R. 2000. Tiled Polygon Traversal Using Half-Plane Edge Functions. In Workshop on Graphics Hardware, ACM SIGGRAPH/Eurographics. Google Scholar

12. MCCORMACK, J., MCNAMARA, B., GIANOS, C., SEILER, L., JOUPPI, N. P., CORELL, K., DUTTON, T., AND ZURAWSKI, J. 1999. Implementing Neon: A 256-Bit Graphics Accelerator. IEEE Micro 19, 2 (March/April), 58–69. Google ScholarDigital Library

13. MOREIN, S. 2000. ATI Radeon HyperZ Technology. In Workshop on Graphics Hardware, Hot3D Proceedings, ACM SIGGRAPH/Eurographics.Google Scholar

14. NVIDIA. 2001. HRAA: High-Resolution Antialiasing Through Multisampling. Tech. rep.Google Scholar

15. PINEDA, J. 1988. A Parallel Algorithm for Polygon Rasterization. In Computer Graphics (Proceedings of ACM SIGGRAPH 88), ACM, 17–20. Google Scholar

16. SHIRLEY, P. 1990. Physically Based Lighting Calculations for Computer Graphics. PhD thesis, University of Illinois at Urbana Champaign. Google Scholar

17. WILLIAMS, L. 1983. Pyramidal Parametrics. In Computer Graphics (Proceedings of ACM SIGGRAPH 83), ACM, 1–11. Google Scholar

18. WOO, R., YOON, C., KOOK, J., LEE, S., AND YOO, H. 2002. A 120-mW 3-D Rendering Engine With a 6-Mb Embedded DRAM and 3.2 GB/s Runtime Reconfigurable Bus for PDA Chip. IEEE Journal of Solid-State Circuits 37, 19 (October), 1352–1355.Google Scholar