“A characterization of ten rasterization techniques” by Gharachorloo, Gupta, Sproull and Sutherland

Conference:

Type(s):

Title:

- A characterization of ten rasterization techniques

Presenter(s)/Author(s):

Abstract:

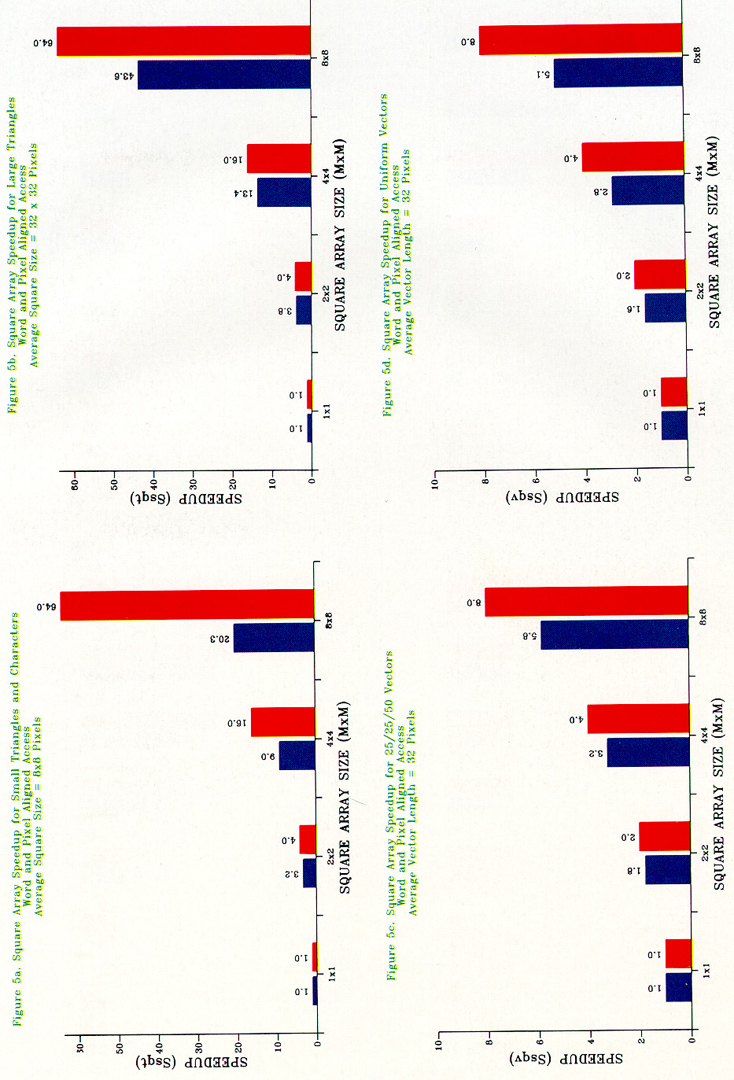

With widespread use of raster scan displays and the ever-increasing desire for faster interactivity, higher image complexity, and higher resolution in displayed images, several techniques have been proposed for rasterizing primitive graphical objects. This paper characterizes the performance of these techniques and shows how they evolve for more complex images on higher resolution displays. This characterization will not only show the strengths and deficiencies of existing rasterization techniques, but will also reveal new architectures for future raster graphics systems.

References:

1. K. Akeley and T. Jermoluk. High Performance Polygon Rendering. Proceedings of SIGGRAPH, 22(4):239-246, August 1988.]]

2. B. Apgar, B. Bersack, and A. Mammen. A Display System for the Stellar Graphics Supercomputer Model GS 1000. Proceedings of SIGGRA PH, 22(4):255-268, August 1988.]]

3. Mike Asai, Graham Short, Tom Preston, Richard Simpson, Derek Roskell, and Karl Guttag. The TI34010 Graphics System Processor. Computer Graphics and Applications, 6(10):24-39, October 1986.]]

4. A. Bechtolsheim and F. Baskett. High-Performance Raster Graphics for Microcomputer Systems. Computer Graphics, 14(3):43-47, July 1980.]]

5. J.E. Bresenham. Algorithm for computer control of a digital plotter. IBM Systems Journal, 4(1):25-30, July 1965.]]

6. J.E. Bresenham. Raster Line Run Length Slice Algorithm, IBM System Communication Division, TR 29.0180, Research Triangle Park, North Carolina. January 1978.]]

7. J.E. Bresenham. Incremental Line Compaction. The Computer Journal, 25(1): 116-120, 1982.]]

8. J.H. Clark. The Geometry Engine: A VLSI Geometry System for Graphics. Computer Graphics, 16(3):127-133, July 1982.]]

9. J.H. Clark and M.R. Hannah. Distributed Processing in a High-Performance Smart Image Memory. LAMBDA (Now VLSI Design), (4th. Quarter):40-45, 1980.]]

10. M. Deering, S. Winner, B. Schediwy, C. Duffy, and N. Hunt. The Triangle Processor and Normal Vector Shader: A VLSI System for High Performance Graphics. Proceedings of SIGGRAPH, 22(4):21-30, August 1988.]]

11. S. Demetrescu. High Speed Image Rasterization Using Scan Line Access Memories. Proc. 1985 Chapel Hill Conference on VLSI, pages 221-243, Computer Science Press, 1985.]]

12. H. Fuchs and J. Poulton. Pixel Planes: A VLSI-Oriented Design for a Raster Graphics Engine. VLSI Design, 2(3):20-28, 3rd. Quarter 1981.]]

13. H. Fuchs, J. Poulton, J. Eyles, T. Greer, J. Goldfeather, D. Ellsworth, S. Molnar, G. Turk, B. Tebbs, and L. israel. A Heterogeneous Multiprocessor Graphics System Using Processor- Enhanced Memories. Proceedings of SIGGRAPH, 1989.]]

14. D. Fussell and B.D. Rathi. A VLSI-Oriented Architecture for Real-Time Raster Display of Shaded Polygons. Proc. of Graphics Interface, pages 373-380, 1982.]]

15. N. Gharachorloo, S. Gupta, E. Hokenek, P. Balasubramanian, B. Bogholtz, C. Mathieu, and C. Zoulas. Subnanosecond Pixel Rendering with Million Transistor Chips. Proceedings of SIGGRAPH, 22(4):41-49, August 1988.]]

16. N. Gharachorloo and C. Pottle. SUPER BUFFER: A Systolic VLSI Graphics Engine for Real Time Raster Image Generation. Proc. 1985 Chapel Hill Conference on VLSI, pages 285-305, Computer Science Press, 1985.]]

17. A. Goris, B. Fredriekson, and H. Baeverstad. A Configurable Pixel Cache for Fast Image Generation. IEEE CGdA, pages 24-32, 1987.]]

18. S. Gupta. Architectures and Algorithms for Parallel Updates of Raster Scan Displays, Computer Science Department, Carnegie-Mellon University, CMU-CS-82-111, Pittsburgh, PA. December 1981.]]

19. S. Gupta, R.F. Sproull, and I.E. Sutherland. A VLSI Architecture for Updating Raster Scan Display. Computer Graphics, 15(3):71-78, July 1981.]]

20. J.H. Jackson. Dynamic Scan-converted Images with a Frame Buffer Display Device. Proceedings of S1GGRAPH, page 163, 1980.]]

21. B.W. Jordan, Jr. and R.C. Barrett. A Cell Organized Raster Display for Line Drawings. Comm. of the ACM, 17(2):676, Febraury 1974.]]

22. M. Kaplan and D. Greenberg. Parallel Processing techniques for Hidden Surface Removal. Proceedings of SIGGRAPH, page 300, August 1979.]]

23. L. Kohn and S.W. Fu. A 1,000,000 Transistor Microprocessor. ISSCC, pages 54-55, February 1989,]]

24. R. Matick, D.T. Ling, S. Gupta, and F.H. Dill. All Points Addressable Raster Display Memory. IBM Journal of Res. and Dev., 28(4):379-382, July 1984.]]

25. W.M. Newmann and R.F. Sproull. Principles of Interactive Computer Graphics. McGraw Hill, 1973.]]

26. H. Niimi, Y. Imai, M. Murakami, S. Tomita, and H. Hagiwara. A Parallel Processor System for Three Dimensional Color Graphics. Proceedings of SIGGRAPH, page 67, July 1984.]]

27. I. Page. Disarray: A 16 x 16 RasterOp processor. Eurographics 83, pages 367-377, Amsterdam: North Holland, 1983.]]

28. F.I. Parke. Simulation and Expected Performance Analysis of Multiple Processor Z-Buffer Systems. Siggraph, pages 48-56, 1980.]]

29. R. Schumacker. A New Visual System Architecture. Proc. of Second Interservice/Industry Training Equipment Conf., page 1, November 1982.]]

30. R.F. Sproull. Using Program Transformations to Derive Line-Drawing Algorithms. ACM Transactions on Graphics, 1 (4):259-273, 1982.]]

31. R.F. Sproull. Frame Buffer Display Architectures. Annual Review of Computer Science, 1 : 19-46, Annual Reviews Inc., 1986.]]

32. R.F. Sproull, I.E. Sutherland, A. Thompson, and S. Gupta. The 8 by 8 Display. A CM Transactions on Graphics, 2(1 ):32-56, January 1983.]]

33. I.E. Sutherland, R.F. Sproull, and R.A. Schumacker. A Characterization of Ten Hidden-Surface Algorithms. Computing Surveys, 6(1): 1, March 1974.]]

34. R.W. Swanson and L.J. Thayer. A Fast Shaded- Polygon Renderer. Proceedings of SIGGRAPH, pages 95-102, 1986.]]

35. C.P. Thacker, E.M. McCreight, B.W. Lampson, R.F. Sproull, and D.R. Boggs. Alto: A Personal Computer”. Computer Structures: Readings and Examples, McGraw Hill, 1981.]]

36. A.M. Walsby. Fast colour raster graphics using an array processor. Eurographics 80, pages 303-313, Amsterdam: North Holland, 1980.]]

37. G.S. Watkins. A Real Time Visible Surface Algorithm, University of Utah, UTEC-CSC-70-101, June 1970.]]

38. R. Weinberg. Parallel Processing Image Synthesis and Anti-Aliasing. Proceedings of SIGGRAPH, pages 147-154, july 1982.]]

39. M.C. Whitton. Memory Design for Raster Graphics Displays. Computer Graphics and Applications, 4(3):48-65, March 1984.]]

40. Paul Winser. 3D Graphics for Consumer Applications- How Realistic Does it Have to Be?. Eurographics, 1988.]]