“A chip for low-cost raster-scan graphic display” by Matherat

Conference:

Type(s):

Title:

- A chip for low-cost raster-scan graphic display

Presenter(s)/Author(s):

Abstract:

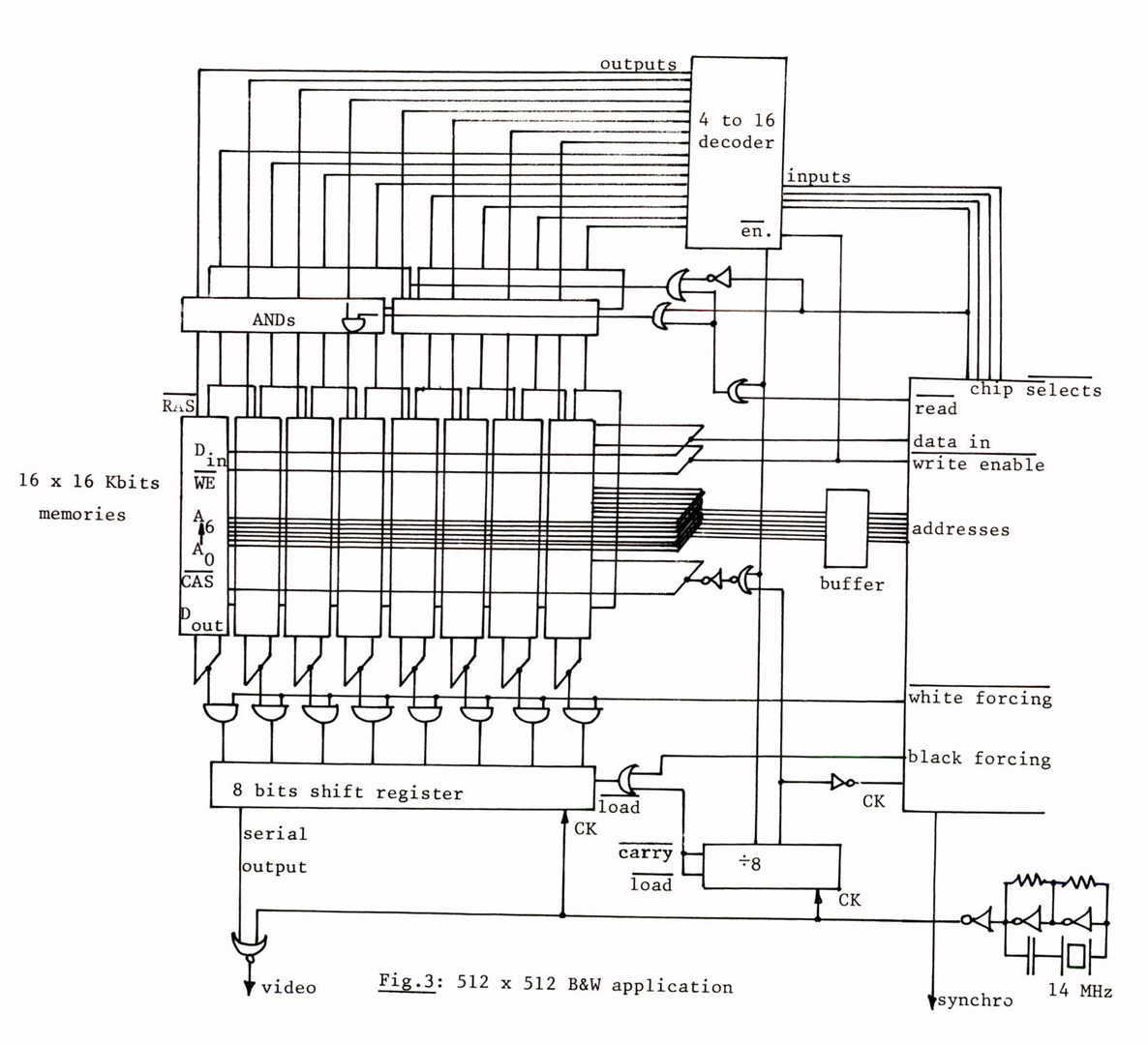

Lowering the cost of graphic display units for use in personnal computers and as time-sharing consoles suggests the use of TV sets. Display electronics for such a raster-scan unit will include a screen memory containing the state of all displayable points, that is up to 256 Kbits for 512 × 512 B&W display and more for colour applications. Technological advances in NMOS memories make such memory sizes cheaper and cheaper. The control part ensuring screen refresh, memory management, vector and character generation, and computer coupling remains very complex. A microprocessor-oriented Large-Scale-Integrated circuit including all these functions has been designed at the Ecole Normale Supérieure. Versatility has guided the design, as well for screen memory organization as for microprocessor interface. Display resolution from 64 × 64 to 512 × 512 are possible, with any number of colours or grey levels, depending only upon the memory size. Microprocessor interface is standard: an eight bits bidirectionnal data bus, a four bits address bus, a read-write signal and an interrupt request. These signals control the vector and character generators which execute microprocessor’s commands during the idle phasis of the display controller. This permits an always clean diplay and yet a decent average speed of one point every 1.3 μs. In addition, a light-pen or crosshair circuitry allows interactive graphic use.

References:

1. Kay, A. C., Microelectronics and the personnal computer. Scientific American, 237 (Sept. 1977), 231-244.

2. Ramtek 9000 Series, Graphic and imagery display systems.

3. Op Het Veld, S. J., Microprocessor-controlled video games, Euromicro 1977.

4. Matrox TV controller family.

5. Motorola catalog, VDG 467 circuit.

6. Matherat, P., Conception d’un circuit intégré pour la visualisation graphique, thèse de 3ème cycle, Institut de Programmation de Paris, Mai 1978.

7. Oberman, R. M. M., A flexible rate multiplier with uniform pulse distribution output, IEEE trans. on Comp., Vol. C-21, (1972), 896.

8. Bresenham, J. E., Algorithm for computer control of a digital plotter, IBM systems J.4, (1965), 25-30.

9. Horn, B. K. P., Circle generators for display devices, Computer graphics and image processing 5, (1976), 280-288.