“VC-1: a scalable graphics computer with virtual local frame buffers” by Nishimura and Kunii

Conference:

Type(s):

Title:

- VC-1: a scalable graphics computer with virtual local frame buffers

Presenter(s)/Author(s):

Abstract:

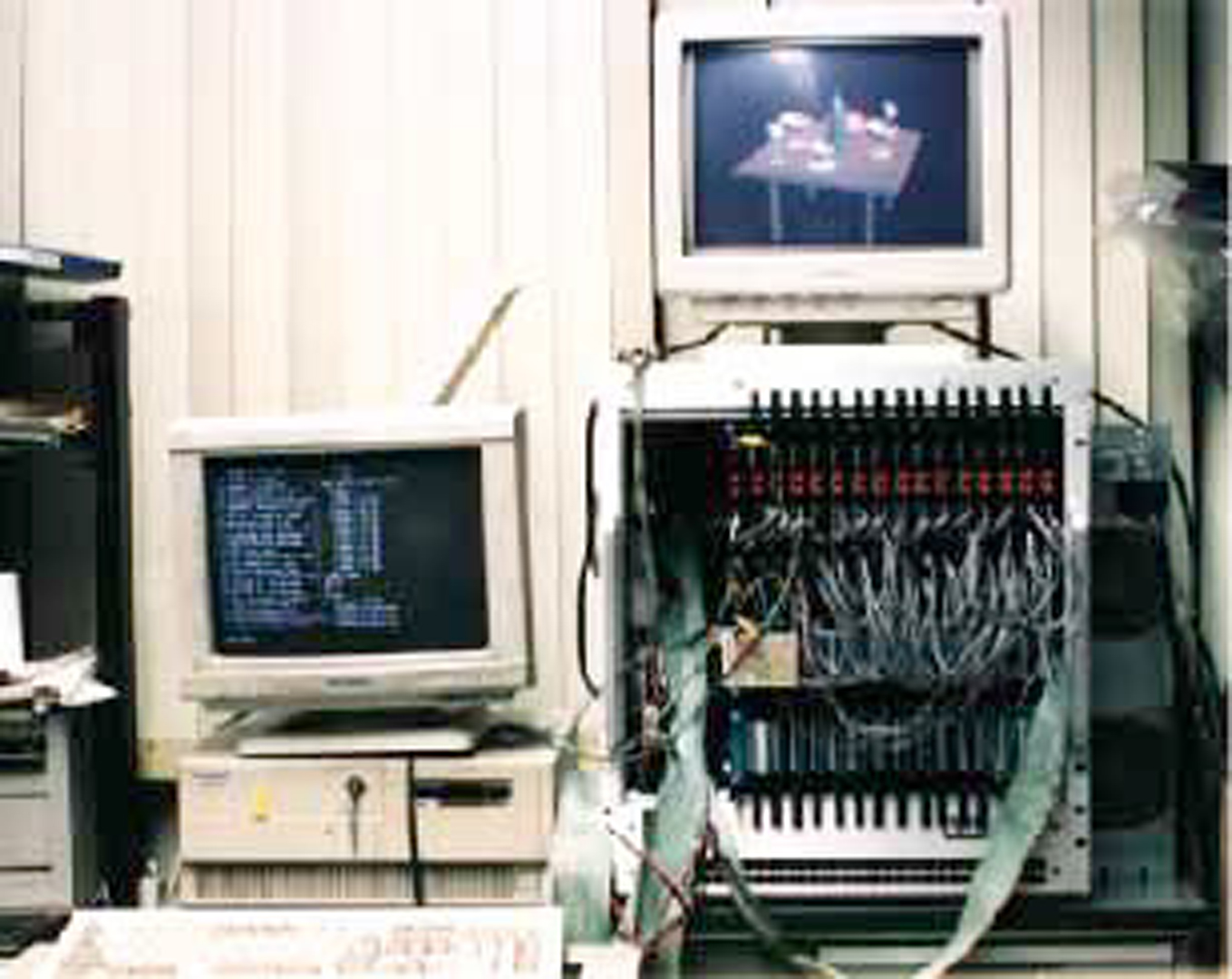

The VC-1 is a parallel graphics machine for polygon rendering based on image composition. This paper describes the architecture of the VC-1 along with a parallel polygon rendering algorithm for it. The structure of the VC-1 is a loosely-coupled array of 16 general-purpose processors, each of which is equipped with a local frame buffer. The contents of the local frame buffers are merged in real time for generating the final image. The local frame buffers are virtualized with a demand-paging technique, by which the image memory capacity for each local frame buffer is reduced to one eighth of full-screen capacity. Polygons are rendered in either pixel parallel or polygon parallel depending on the on-screen area of each polygon. The real performance of the VC-1 as well as estimated performance for systems with up to 256 processors is shown.

References:

1. AKELEY, K. RealityEngine Graphics. Proceedings of SIG- GRAPH ’93 (August 1993), 109-116.

2. COHEN, D., AND DEMETRESCU, S. A VLSI approach to Computer Image Generation. Tech. rep., Information Sciences Institute, University of Southern California, 1979.

3. Cox, M. Algorithms for Parallel Rendering. PhD thesis, Dept. of Computer Science, Princeton University, 1995.

4. DEERING, M., WINNER, S., SCHEDIWY, B., DUFFY, C., AND HUNT, N. The Triangle Processor and Normal Vector Shader: A VLSI System for High Performance Graphics. ACM Computer Graphics 22, 4 (August 1988), 21-30.

5. ELLSWORTH, D., GOOD, H., AND TEBBS, B. Distributing Display Lists on a Multicomputer. ACM Computer Graphics 24, 2 (March 1990), 147-154.

6. HAEBERLI, P., AND AKELEY, K. The Accumulation Buffer: Hardware Support for High-Quality Rendering. ACM Computer Graphics 24, 4 (August 1990), 309-318.

7. KUBOTA COMPUTER INC. TITAN2 Technical Overview, 1993.

8. MOLNAR, S. Combining Z-buffer Engines for Higher-Speed Rendering. In Advances in Computer Graphics Hardware III (1988), Springer Verlag, pp. 171-182.

9. MOLNAR, S., Cox, M., ELLSWORTH, D., AND FUCHS, H. A sorting classification of parallel rendering. IEEE Computer Graphics and Applications 14, 4 (July 1994), 23-32.

10. MOLNAR, S., EYLES, J., AND POULTON, J. PixelFlow: High-Speed Rendering Using Image Composition. ACM Computer Graphics 26, 2 (July 1992), 231-240.

11. NISHIMURA, S. A Parallel Architecture for Computer Graphics Based on the Conflict-Free Multiport Frame Buffer. Doctoral dissertation, Dept. of Information Science, Faculty of Science, The University of Tokyo, 1995.

12. PALOVUORI, K. An Implementation of an Linearly Expandable Graphics Processing Architecture. Tech. Rep. 8-94, Dept. of Electrical Engineering, Tampere University of Technology, Finland, 1994.

13. ROMAN, G. C., AND KIMURA, T. VLSI perspective of real-time hidden-surface elimination. Computer-Aided Design 13, 2 (March 1981), 99-107.

14. SCHNEIDER, B.-O. A Processor for an Object-Oriented Rendering System. Computer Graphics Forum 7, 4 (1988), 301-310.

15. SHAW, C. D., GREEN, M., AND SCHAEFFER, J. A VLSI Architecture for Image Composition. In Advances in Computer Graphics Hardware III (1988), Springer Verlag, pp. 183-199.

16. WEINBERG, R. Parallel Processing Image Synthesis and Anti-Aliasing. ACM Computer Graphics 15, 3 (August 1981), 55-62.