“Chap – a SIMD graphics processor” by Levinthal and Porter

Conference:

Type(s):

Title:

- Chap - a SIMD graphics processor

Presenter(s)/Author(s):

Abstract:

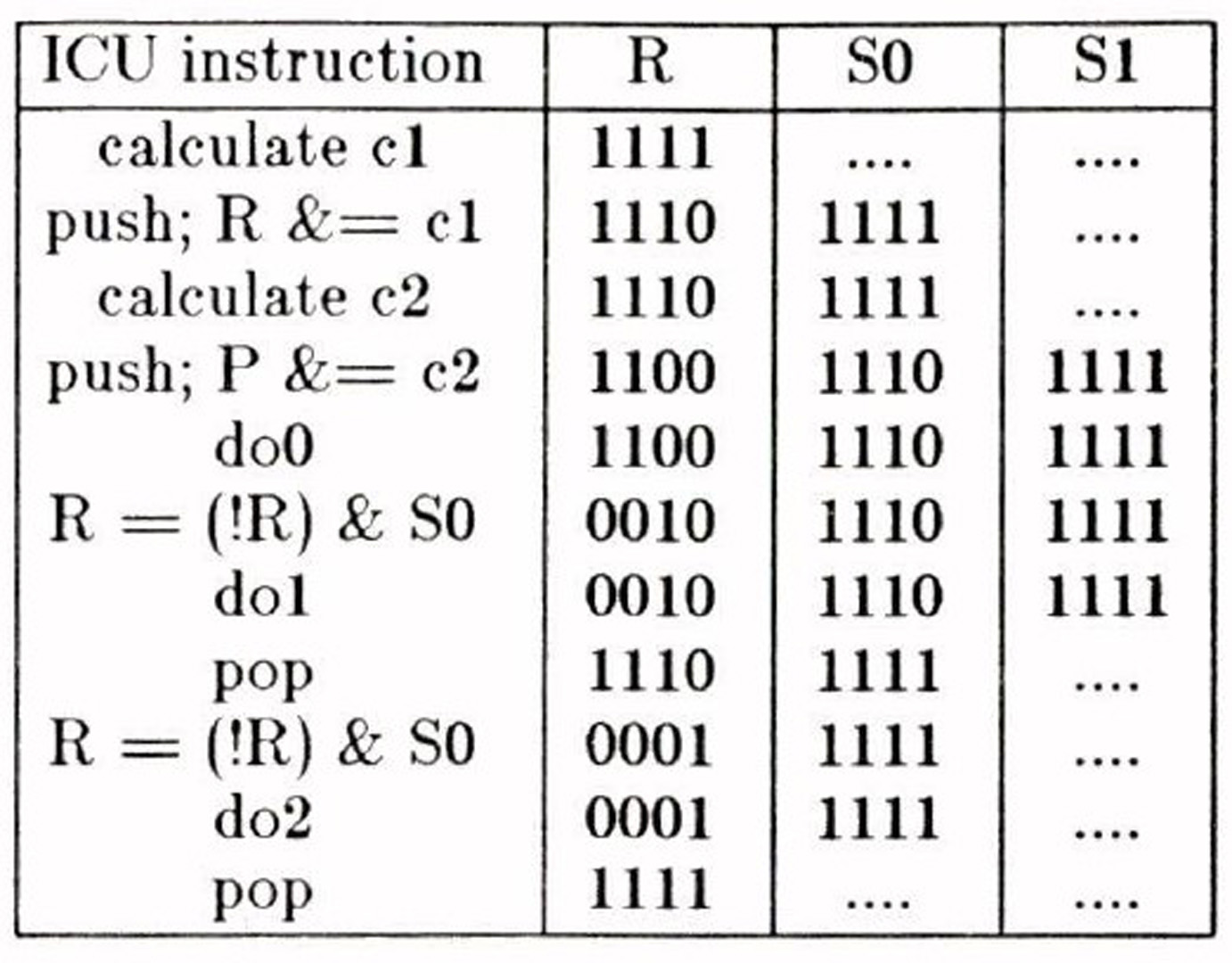

Special purpose processing systems designed for specific applications can provide extremely high performance at moderate cost. One such processor is presented for executing graphics and image processing algorithms as the basis of a digital film printer. Pixels in the system contain four parallel components: RGB for full color and an alpha channel for retaining transparency information. The data path of the processor contains four arithmetic elements connected through a crossbar network to a tessellated scratchpad memory. The single instruction, multiple data stream (SIMD) processor executes instructions on four pixel components in parallel. The instruction control unit (ICU) maintains an activity stack for tracking block-structured code, using data-dependent activity flags for conditional disabling subsets of the ALUs. Nested loops and if-then-else constructs can be programmed directly, with the ICU disabling and reenabling ALUs on the basis of their individual status bits.

References:

1. Barnes, G., et all, The ILLIAC IV Computer. IEEE Transactions on Computers Vol C-17, No 8 (August 1968), pp 746-757.

2. Fielding, R., The Technique of Special Effects Cinematography. Hastings House, New York, 1977.

3. Kubo, M., Taguchi, Y., Agusa, K., Ohno, Y., A multi-microprocessor system for three dimensional color graphics. Proc of IFIP 80, 1980.

4. Leffler, S., Chap Assembler Reference Manual. Technical Memo 98, Computer Division, Lucasfilm Ltd, December, 1983.

5. Leffler, S., Chap Runtime Monitor Reference Manual. Technical Memo 102, Computer Division, Lucasfilm Ltd, December, 1983.

6. Porter, T., Matte Box Design. Technical Memo 63, Computer Division, Lucasfilm Ltd, August 1983.

7. Porter, T., Duff, T., Compositing Digital Images. Computer Graphics Vol 18, No 3, 1984, To be published

8. Shapiro, H. D. Theoretical Limitations on the Efficient Use of Parallel Memories. IEEE Transactions on Computers, Vol C-27, No. 5 (May 1978),.