“FBRAM: a new form of memory optimized for 3D graphics” by Deering, Schlapp and Lavelle

Conference:

Type(s):

Title:

- FBRAM: a new form of memory optimized for 3D graphics

Presenter(s)/Author(s):

Abstract:

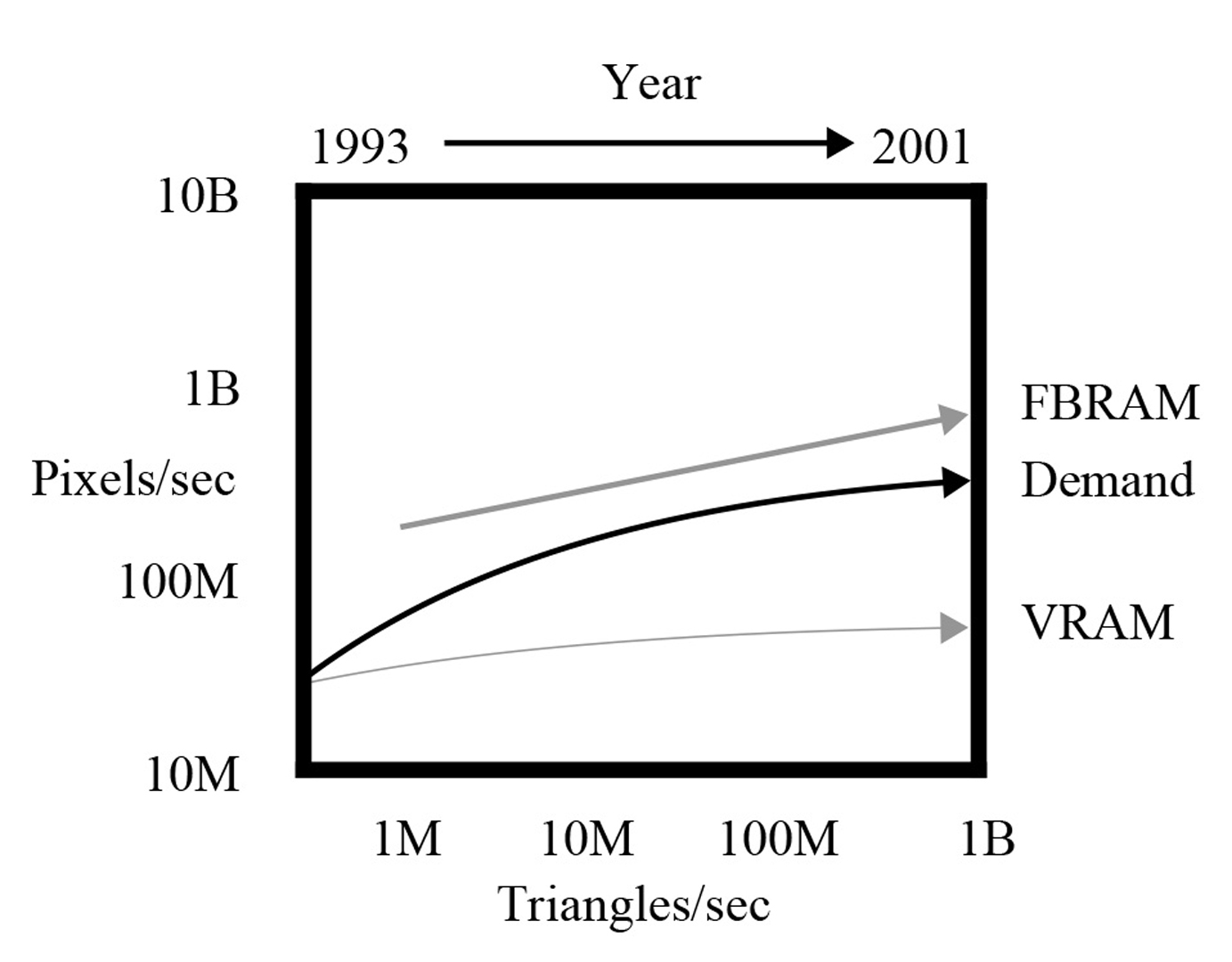

FBRAM, a new form of dynamic random access memory that greatly accelerates the rendering of Z-buffered primitives, is presented. Two key concepts make this acceleration possible. The first is to convert the read-modify-write Z-buffer compare and RGBα blend into a single write only operation. The second is to support two levels of rectangularly shaped pixel caches internal to the memory chip. The result is a 10 megabit part that, for 3D graphics, performs read-modify-write cycles ten times faster than conventional 60 ns VRAMs. A four-way interleaved 100MHz FBRAM frame buffer can Z-buffer up to 400 million pixels per second. Working FBRAM prototypes have been fabricated.

References:

1. Akeley, Kurt and T. Jermoluk. High-Performance Polygon Rendering, Proceedings of SIGGRAPH ’88 (Atlanta, GA, Aug 1-5, 1988). In Computer Graphics 22, 4 (July 1988), 239-246.

2. Akeley, Kurt. Reality Engine Graphics. Proceedings of SIG-GRAPH ’93 (Anaheim, California, August 1-6, 1993). In Computer Graphics, Annual Conference Series, 1993, 109- 116.

3. Catmull, E. A Subdivision Algorithm for Computer Display of Curved Surfaces, Ph.D. Thesis, Report UTEC-CSc-74-133, Computer Science Dept., University of Utah, Salt Lake City, UT, Dec. 1974.

4. Deering, Michael, S. Winner, B. Schediwy, C. Duffy and N. Hunt. The Triangle Processor and Normal Vector Shader: A VLSI system for High Performance Graphics. Proceedings of SIGGRAPH ’88 (Atlanta, GA, Aug 1-5, 1988). In Computer Graphics 22, 4 (July 1988), 21-30.

5. Deering, Michael, and S. Nelson. Leo: A System for Cost Ef-fective Shaded 3D Graphics. Proceedings of SIGGRAPH ’93 (Anaheim, California, August 1-6, 1993). In Computer Graphics, Annual Conference Series, 1993, 101-108.

6. Deering, Michael. Data Complexity for Virtual Reality: Where do all the Triangles Go? Proceedings of IEEE VRAIS ’93 (Seattle, WA, Sept. 18-22, 1993). 357-363.

7. Demetrescu, S. A VLSI-Based Real-Time Hidden-Surface Elimination Display System, Master’s Thesis, Dept. of Com-puter Science, California Institute of Technology, Pasadena CA, May 1980.

8. Demetrescu, S. High Speed Image Rasterization Using Scan Line Access Memories. Proceedings of 1985 Chapel Hill Con-ference on VLSI, pages 221-243. Computer Science Press, 1985.

9. Fuchs, Henry, and J. Poulton. Pixel Planes: A VLSI-Orient-ed Design for a Raster Graphics Engine. In VLSI Design, 2,3 (3rd quarter 1981), 20-28.

10. Foley, James, A. van Dam, S. Feiner and J Hughes. Com-puter Graphics: Principles and Practice, 2nd ed., Addison-Wesley, 1990.

11. Gharachorloo, Nader, S. Gupta, E. Hokenek, P. Bala-subramanina, B. Bogholtz, C. Mathieu, and C. Zoulas. Subnanosecond Rendering with Million Transistor Chips. Proceedings of SIGGRAPH ’88 (Boston, MA, July 31, Aug 4, 1989). In Computer Graphics 22, 4 (Aug. 1988), 41-49.

12. Gharachorloo, Nader, S. Gupta, R. Sproull, and I. Suther-land. A Characterization of Ten Rasterization Techniques. Proceedings of SIGGRAPH ’89 (Boston, MA, July 31, Aug 4, 1989). In Computer Graphics 23, 3 (July 1989), 355-368.

13. Goris, A., B. Fredrickson, and H. Baeverstad. A Config-urable Pixel Cache for Fast Image Generation. In IEEE CG&A 7,3 (March 1987), pages 24-32, 1987.

14. Harrell, Chandlee, and F. Fouladi. Graphics Rendering Ar-chitecture for a High Performance Desktop Workstation. Pro-ceedings of SIGGRAPH ’93 (Anaheim, California, August 1- 6, 1993). In Computer Graphics, Annual Conference Series, 1993, 93-100.

15. M5M410092 FBRAM Specification. Mitsubishi Electric, 1994.

16. Molnar, Steven, J. Eyles, J. Poulton. PixelFlow: High-Speed Rendering Using Image Composition. Proceedings of SIG-GRAPH ’92 (Chicago, IL, July 26-31, 1992). In Computer Graphics 26, 2 (July 1992), 231-240.

17. Patterson, David, and J. Hennessy. Computer Architecture: a Quantitative Approach, Morgan Kaufmann Publishers, Inc., 1990.

18. Pinkham, R., M. Novak, and K. Guttag. Video RAM Excels at Fast Graphics. In Electronic Design 31,17, Aug. 18, 1983, 161-182.

19. Sproull, Robert, I. Sutherland, and S. Gupta. The 8 by 8 Display. In ACM Transactions on Graphics 2, 1 (Jan 1983), 35-56.

20. Whitton, Mary. Memory Design for Raster Graphics Dis-plays. In IEEE CG&A 4,3 (March 1984), 48-65, 1984.